# A Parallel Programming Tool-flow for SDR Signal Processing using Heterogeneous Architectures

Lerato J. Mohapi Supervised By: Dr. Simon Winberg

> University of Cape Town Department of Electrical Engineering Software Defined Radio Group

#### HPSPSA 2014

January 31, 2014

Title: A Parallel Programming Tool-flow for Software Defined Radio

Author: Lerato J. Mohapi

Institute: UCT

1/18

# **OUTLINE**

Introduction

**METHODOLOGY**

Parallel Programming Tool-flow

RESULTS

**CONCLUSIONS**

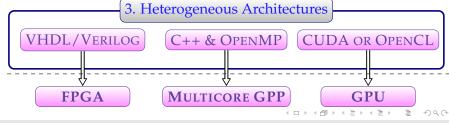

#### INTRODUCTION

\* A Domain Specific Language (DSL) for SDR: SDR-DSL

\* Need to facilitate parallel programming of Heterogeneous Archs.

INTRODUCTION METHODOLOGY Parallel Programming Tool-flow

#### Parallel Programming Tool-flow RESULTS CONCLUSIONS

#### Introduction

\* DSL - Constructs tailored towards a Domain

\* Expressiveness & Ease of use for heterogeneous archs.

) Q (

Institute: UCT

CONCLUSIONS

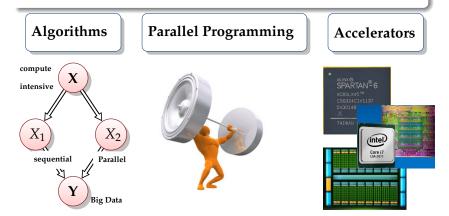

2. Parallel Programming

Algorithms and Accelerators => Verbose + Concurrent LPL

# INTRODUCTION: OBJECTIVES AND SCOPE

• intuitive Parallel Programming tool-flow for HCA

- Single source => Multiple heterogeneous targets

- Auto Parallelize and Validate DSP algorithms

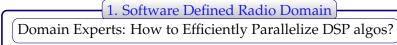

#### INTRODUCTION: SDR AND HETEROGENIETY

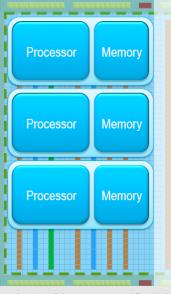

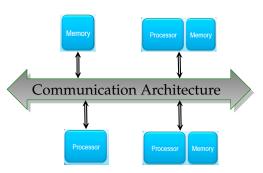

- Hardware/Application Level Heterogeniety

- Each PE Optimized to perform different task

- Each Processor exploit parallelism • Multiple chips, single platform

- Sequencial and Parallel instruction sets

Figure: Overview of interoperability in HCA

CONCLUSIONS

### METHODOLOGY OUTLINE

- SDR-DSL Development Steps:

- Refine Requirements

- Study SDR DSP algorithms

- Build SDR-DSL Compiler: Delite

- Walidate

INTRODUCTION

6 Case study: Wideband Channelization

- Several individual DSP modules, thus spiral model of software development

- Permits iterative SDR-DSL development and cyclic progress assessment

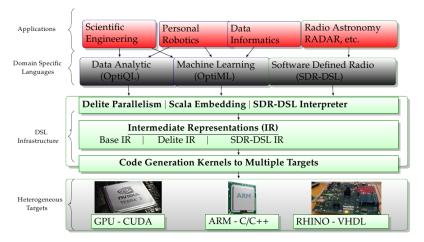

### METHODOLOGY: DELITE APPROACH

Figure: Delite framework - Common parallel execution patterns to ease DSL development - Runtime management (Sched. & Synch.)

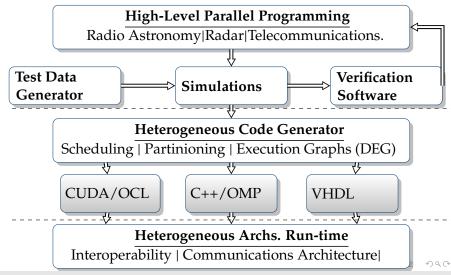

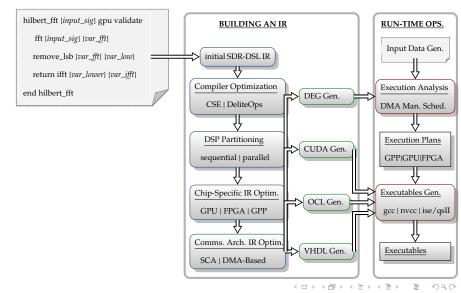

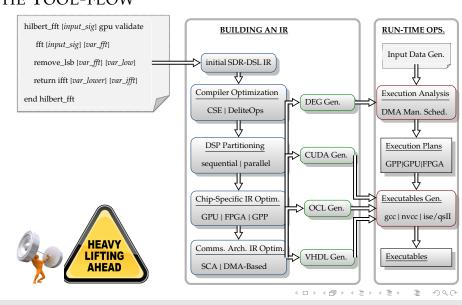

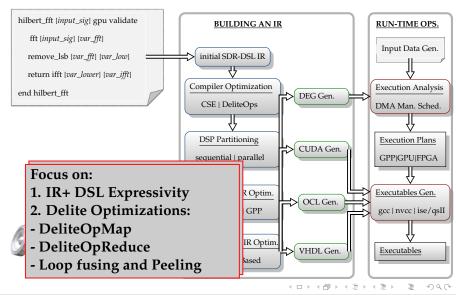

#### THE TOOL-FLOW

### THE TOOL-FLOW

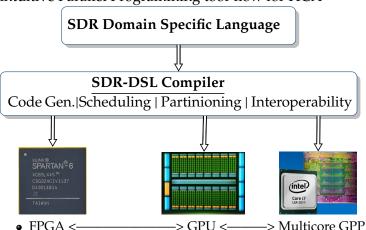

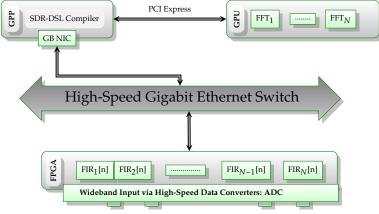

# RESULTS: TARGET CASE STUDY

Figure: Real-time HCA for Wideband SDR channelization using FPGA-Based pipelined FIR filters, and GPU-based Spectral Analysis using FFTs

# Listing 1: FIR filter implementation

```

object HTransformerRunner extends OptiMLApplicationRunner

with FIRFilter with KaizerWin with SineGenerator

trait FIRFilter extends OptiMLApplication

def main() = {

DSP Constructs embedded in Scala

// Get Coefficients of Length = 63

val FCoefficients =

ConstFloatingPointFilterCoefficients()

// Prep. Data Length and Tap Order

val SLength = 993

val FTapOrder = 62

val K = SLength - FTapOrder + 1

val FInput = GenerateSignal(SLength)

val FOutput= DenseVector[Double] (K, true)

for(SHIndex <- 0 until K){

var tmpvals = FInput(SHIndex::FTapOrder+SHIndex)

FOutput (SHIndex) =

FIRFilter (FCoefficients, tmpvals, FTapOrder)

```

Expressivity

Validation

Test Data + DeliteFileReader - Need For Plotting

println (FOutput (SHIndex))

# RESULTS: CODE GENERATION

#### Listing 2: Generated CUDA Kernel

```

// CUDA Kernel Generated by Delite

texture<float, 1, cudaReadModeElementType> KaizerCoeffs;

__qlobal__ void fir(float *d_VAL_A,float* Output_Data, const

unsigned int TapOrder, const unsigned int J) {

// Shared memory, the size is determined by the host application

extern __shared__ float OutputData[];

// Perform FIR

for (j=0; j<J; j++) {

for (i=0: i<TapOrder: ++i) {

sum += (float) ((float) tex1D(KaizerCoeffs, (unsigned

int)i ) * d VAL A[(unsigned int)(i+tid+TapOrder*j +

bid*J*TapOrder)]);

syncthreads();

OutputData[tid+TapOrder*j] = (float)sum;

__syncthreads();

sum = (double) 0.0;

```

CUDA Kernels

#### The Kernel

- Implements FIR

- Declare Textures

- Declare Shared memory

- Synchronize Threads

16/18

Author: Lerato J. Mohapi Institute: UCT

# CONCLUSIONS AND FURTHER WORK

- Work Done

- Requirements refined, and SDR Domain Knowledge

- SDR-DSL Syntax and Initial IR Implemented Using Delite (Borrowed Some OptiML Constructs)

- Through its data types and execution semantics, SDR-DSL will reflects the desired abstraction hierarchy in SDR

- Work to be Done

- Modify Code Generator

- SDR-DSL Tool-flow Planned to include SDF and CSDF

- SDR-DSL facilitates SDR signal processing on heterogeneous architectures

In Summary: SDR-DSL is expected to be hetegeneous PPTF that divides signal processing algorithms into sequential and parallel patterns while allowing designers to realize the performance of their applications by exploring different design parameters.

900

Institute : UCT

INTRODUCTION METHODOLOGY Parallel Programming Tool-flow RESULTS CONCLUSIONS

\*\*\*\*\*\*\* Thank you! \*\*\*\*\*\*\*

\*\*\*\*\*\*\* Questions? \*\*\*\*\*\*\*\*

990

Title: A Parallel Programming Tool-flow for Software Defined Radio

Author: Lerato J. Mohapi

Institute: UCT